Традиційно продуктивність чипів збільшувалася за рахунок зростання кількості транзисторів у них. Але сучасна електроніка досягла ліміту технології виробництва і уже кілька років «топчеться» на місці – фактична кількість транзисторів на кожному квадратному міліметрі процесорів залишається майже незмінною. Однак у Intel і TSMC придумали, як продовжити нарощувати кількість транзисторів у чипі, якщо неможливо зменшувати розмір окремого транзистора. Їхня відповідь – транзистори CFET.

Intel і TSMC збираються оприлюднити деталі про нову конструкцію транзисторів. Ці два гіганти індустрії планують замінити використовувані сьогодні транзистори з кільцевим затвором (Gate All-around) на вертикально розміщені комплементарні польові транзистори (CFET). Тобто CFET – це наче багатоповерхівка з поверхами-транзисторами, тоді як попередні дизайни транзисторів були виключно «одноповерховими».

Концепція CFET, яка передбачає накладання шарів транзисторів n- та p-типу один на одного, була вперше представлена дослідницьким інститутом IMEC у 2018 році. Хоча більшість ранніх досліджень проводилися в академічних колах, комерційні компанії, такі як Intel і TSMC, зараз наважилися на їхнє впровадження і активно досліджують цей тип транзисторів нового покоління.

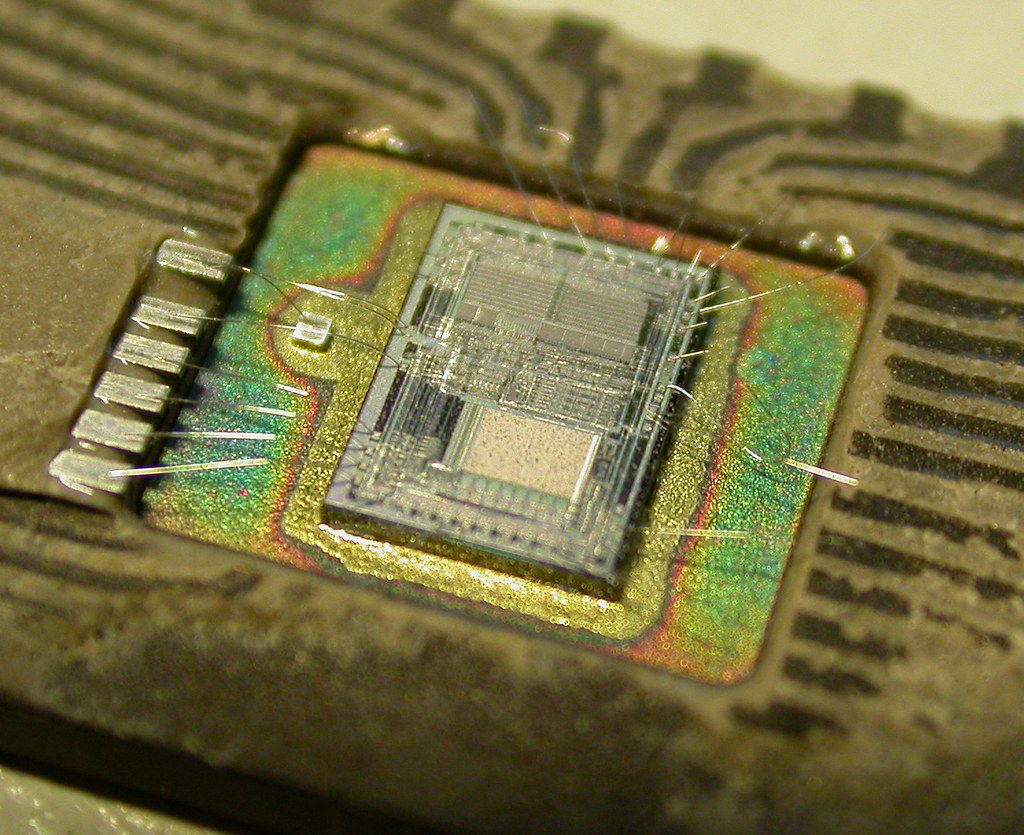

Дослідники Intel створили монолітний 3D CFET, який містить три нанострічки n-FET, розміщені над трьома нанострічками p-FET, зберігаючи вертикальний зазор 30 нм.

У презентації Intel під назвою « Демонстрація інвертора багатошарової КМОП із кроком затвора 60 нм із живленням через і прямими контактами заднього пристрою» описано функціональні тестові схеми інвертора з використанням CFET із кроком затвора 60 нм. Ця конструкція також має вертикально-шарову епітаксію з подвійним джерелом-стоком і подвійні стеки з металевими затворами, а також включає в себе систему живлення PowerVia, в якій дроти підключаються із зворотної сторони чипа.

TSMC також представила дизайн CFET, розроблений для логічної технології та з кроком затвора 48 нм. Конструкція акцентує увагу на багатошарових нанопластових транзисторах n-типу, розміщених поверх аналогів p-типу, які можуть похвалитися дивовижним співвідношенням струмів увімкнення/вимкнення, яке охоплює шість порядків величини.

За даними компанії, транзистори TSMC довели свою довговічність, понад 90% успішно витримали випробування. Хоча компанія визнає, що для повного використання можливостей технології CFET необхідно освоїти більше функцій. Поточна робота є ключовим кроком на шляху до цієї мети.

CFET вносить значну зміну в конструкцію транзисторів, завдяки їх вертикальному стекуванню. Це дозволяє двом транзисторам розміститися в межах одного місця, тим самим збільшуючи щільність транзисторів на мікросхемі. Ця конструкція не тільки прокладає шлях до підвищення ефективності використання простору, але також сприяє більш раціональному компонуванню логічної схеми, сприяючи підвищенню ефективності проектування.

Крім того, структура CFET може призвести до зменшення паразитних ефектів, пропонуючи потенційні покращення продуктивності та енергоефективності чипів. Їхні адаптивні конструктивні можливості, як-от здатність збалансувати варіації каналів NMOS і PMOS, у поєднанні з інноваціями, такими як зворотне живлення PowerVia, ще більше оптимізують виробничий процес, роблячи CFET багатообіцяючою розробкою в області транзисторних технологій.