Традиционно производительность чипов увеличивалась за счет роста количества транзисторов в них. Но современная электроника достигла лимита технологии производства и уже несколько лет «топчется» на месте – фактическое количество транзисторов на каждом квадратном миллиметре процессоров остается почти неизменным. Однако у Intel и TSMC придумали, как продолжить наращивать количество транзисторов в чипе, если невозможно уменьшать размер отдельного транзистора. Их ответ – транзисторы CFET.

Intel и TSMC собираются обнародовать детали о новой конструкции транзисторов. Эти два гиганта промышленности планируют заменить используемые сегодня транзисторы с кольцевым затвором (Gate All-around) на вертикально размещенные комплементарные полевые транзисторы (CFET). То есть CFET – это как многоэтажка с этажами-транзисторами, тогда как предыдущие дизайны транзисторов были исключительно «одноэтажными».

Концепция CFET, предполагающая наложение слоев транзисторов n- и p-типа друг на друга, была впервые представлена исследовательским институтом IMEC в 2018 году. Хотя большинство ранних исследований проводились в академических кругах, коммерческие компании, такие как Intel и TSMC, сейчас решились на их внедрение и активно исследуют этот тип транзисторов нового поколения.

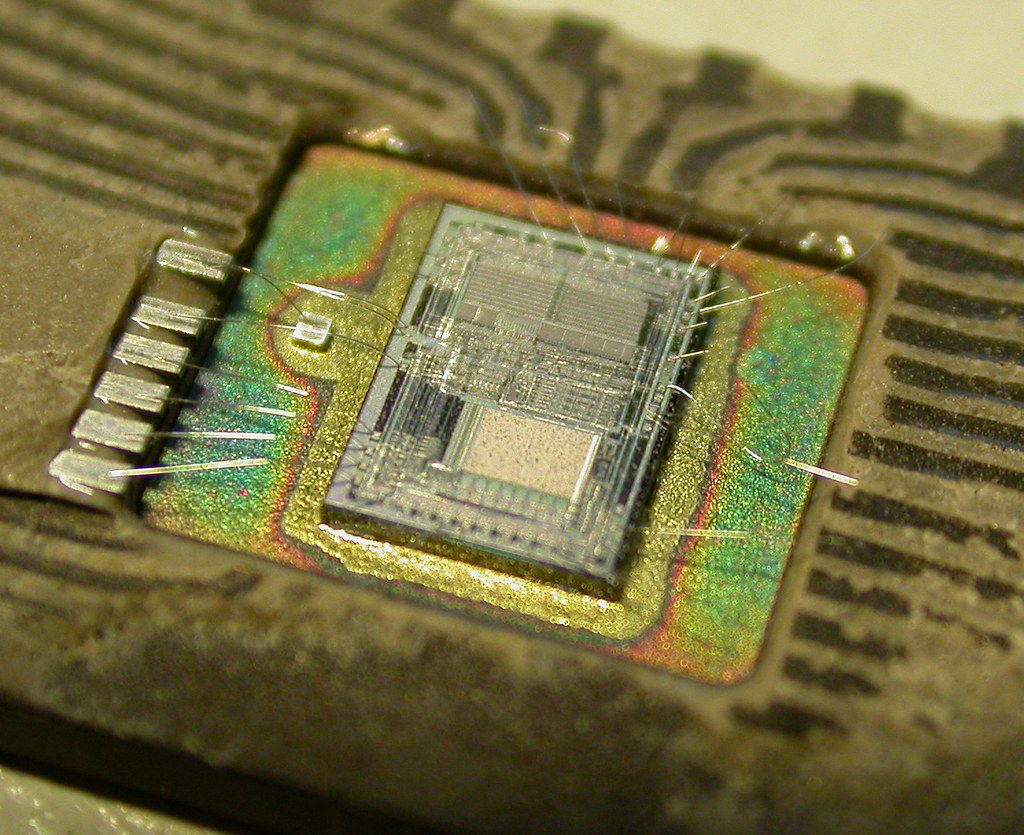

Исследователи Intel создали монолитный 3D CFET, содержащий три нанолента n-FET, расположенные над тремя нанолентами p-FET, сохраняя вертикальный зазор 30 нм.В презентации Intel под названием «Демонстрация инвертора многослойной КМОП с шагом 60 нм затвора с питанием через и прямыми контактами заднего устройства» описаны функциональные тестовые схемы инвертора с использованием CFET с шагом затвора 60 нм. Эта конструкция также имеет вертикально-слойную эпитаксию с двойным источником-стоком и двойные стеки с металлическими затворами, а также включает систему питания PowerVia, в которой провода подключаются с обратной стороны чипа.

TSMC также представила дизайн CFET, разработанный для логической технологии с шагом затвора 48 нм. Конструкция акцентирует внимание на многослойных транзисторах нанопластовых n-типа, размещенных поверх аналогов p-типа, которые могут похвастаться удивительным соотношением токов включения/выключения, охватывающего шесть порядков величины.

По данным компании, транзисторы TSMC доказали свою долговечность, более 90% успешно выдержали испытание. Хотя компания признает, что для полного использования возможностей технологии CFET необходимо освоить больше функций. Текущая работа является ключевым шагом на пути к этой цели.

CFET вносит значительное изменение в конструкцию транзисторов, благодаря их вертикальному стеканию. Это позволяет двум транзисторам разместиться в пределах одного места, тем самым увеличивая плотность транзисторов на микросхеме. Эта конструкция не только прокладывает путь к повышению эффективности использования пространства, но также способствует более рациональной компоновке логической схемы, способствуя повышению эффективности проектирования.Кроме того, структура CFET может привести к уменьшению паразитных эффектов, предлагая потенциальные улучшения производительности и энергоэффективности чипов. Их адаптивные конструктивные возможности, например способность сбалансировать вариации каналов NMOS и PMOS, в сочетании с инновациями, такими как обратное питание PowerVia, еще больше оптимизируют производственный процесс, делая CFET многообещающей разработкой в области транзисторных технологий.