Смартфони з потужністю суперкомп’ютерів (мобільник сьогодні в 5000 разів потужніший за CRAY-2), штучний інтелект, фотографії на сотні мегапікселів та багато інших обчислювальних задач стали можливими завдяки понад півсторіччю шаленого нарощування продуктивності процесорів. Багато в чому таке нарощування стало можливим внаслідок регулярного зменшення розмірів транзисторів. Однак нині технологія дійшла фізичної межі – нанометри закінчилися. На порозі ера ангстрема і в ній все стане дивним.

Оскільки виробництво чипів за технологічними нормами 3 нанометри досягає зрілості, а 2 нанометри вже на шляху до комерційного запровадження, найбільш технологічний виробник чипів компанія TSMC, як повідомляється, закладає основу для наступного логічного кроку – фабрики по випуску процесорів за технологічними нормами в 1 (один) нанометр.

За даними тайванських ЗМІ, TSMC має на меті створити передовий набір мікросхем у Науковому парку Цзяї острівної держави, плануючи виробляти найсучасніші мікросхеми на основі 1-нм техпроцесу.

Samsung нарощує виробництво за 3-нм техпроцесом і планує розгорнути 2-нм техпроцес у 2025 році, а техпроцес Intel 20A наступного покоління, що відповідає 20 ангстремам або приблизно два нанометра, має дебютувати пізніше цього року, якщо не буде затримок.

Ця новина служить нагадуванням про те, що нанометрова ера виробництва напівпровідників, в якій людство живе принаймні з 1990-х, швидко наближається до кінця. Це стосується топових найпродуктивніших чипів, стандартні мікроконтролери, силова та аналогова електроніка, нескладні та застарілі мікросхеми та інші подібні продукти залишатимуться на старих виробничих процесах ще деякий час

Але в той час як нанометри та ангстреми використовують для опису вдосконалення технології виробничого процесу, фізичне значення нанометрів значно змінилося за останнє десятиліття. Фактичне зменшення розмірів транзисторів припинилося десь на етапі 45 нанометрів. Виробникам доводиться шукати нові технології для підвищення продуктивності чипів.

Від вимірювання лінійкою до маркетингових розмірів

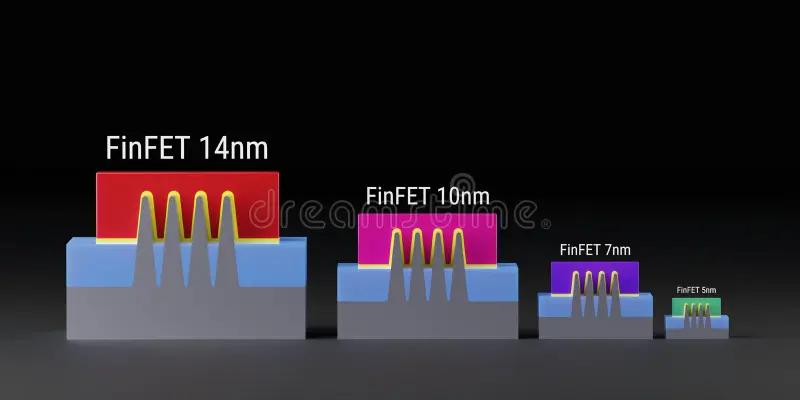

До 2011 року більшість чипів використовували планарні транзистори та нанометри для опису фізичної довжини затвора, і, отже, вказуючи розмір в нанометрах можна було приблизно уявити розмір окремого транзистора в процесорі.

Перехід до транзисторів FinFET приблизно в цей час зробив нанометри невідповідним описом, але практика використання нанометрів продовжувалася, щоб демонструвати користувачам послідовний прогрес. Сьогодні нанометри – це віртуальний символ еквівалентної щільності.

Генеральний директор Intel Пет Гелсінгер підкреслив цей момент як виправдання для ребрендингу власних технологічних процесів для кращої відповідності назвам техпроцесів TSMC і Samsung невдовзі після свого повернення у 2021 році.

Саме з таким маркетинговим трюком несподівано 10-нм техпроцес Intel став Intel 7, а 7-нм техпроцес — Intel 4 і Intel 3. Це тому, що в той час TSMC і Samsung опановували саме техпроцеси 4 та 3 нанометри.

Незважаючи на те, що це явно маркетинговий трюк, спрямований на те, щоб відвернути увагу від факту відставання Intel у виробничих можливостях, Гелсінгер також не помилився. Нанометр як метрика для технологічних процесів є маркетинговим інструментом для опису вдосконалення щільності транзисторів, і, враховуючи цей факт, ребрендинг був розумним кроком.

Але, оскільки нанометри лише приблизно описують відносну щільність і немає стандартизації, порівняння нанометрів одного виробника з такими ж нанометрами іншого виробника стає набагато складнішим.

Ключовим фактором є те, що коли ми намагаємося зменшити FinFET, щоб упакувати більше транзисторів у кремнієві кристали, щоб надати користувачам продуктивніші процесори, ми вже не можемо цього зробити економічно вигідно. Технологія виробництва досягла точки зменшення віддачі. Через фізичні особливості все важче досягти вищої продуктивності з розумним енергоспоживанням.

Процесори наступного покоління використовуватимуть транзистори Gate All-Around (GAA) або те, що Intel назвала RibbonFET.

Ви можете розглядати транзистор RibbonFET або GAA як звичайний FinFET з не одним каналом витоку-стоку, що проходить через ребристий затвор, а набором окремих стрічок каналів, які проходять через одне ребро затвора. Це збільшує площу поверхні, де канал зустрічається з затвором, зменшуючи витік струму, і дозволяє інженерам додатково зменшити транзистори життєздатним способом. Це підвищує щільність транзисторів, що для користувачів зазвичай означає кращу продуктивність без катастрофічної енергоефективності.

У 3-нм техпроцесі Samsung уже використовується ця технологія, тоді як Intel 20A та майбутні 2-нм техпроцеси TSMC впровадять цю техніку.

Низько звисаючі фрукти зникли

Покращення способу упаковки чипів і доставки електричного живлення до них допомогло компенсувати проблему щільності FinFET серед інших переваг. Але це все ще великі енергоємні матриці транзисторів.

Якщо не можна зменшувати розмір транзистора, щоб процесор отримав більше транзисторів, можна збільшити розмір самого чипа для нарощування його продуктивності. Але і в цьому напрямку технології дійшли межі.

Графічний процесор Nvidia H100 площею 814 мм2 , наприклад, близький до межі виробничих технологій. Окрім цього, оскільки ви можете розмістити лише невелику кількість на пластину-заготовку, деякі чипи так чи інакше будуть дефектними, що підвищує вартість кожного чипа.

Ось чому розробники чипів все більше покладаються на вдосконалене пакування, щоб об’єднати кілька менших чиплетів в один великий центральний або графічний процесор у пакеті.

Сімейство Zen від AMD і карти GPU Max від Intel є яскравими прикладами того, що можливо за допомогою розширеного пакетування.

Однак, мабуть, більш цікавий розвиток відбувається навколо доставки електроенергії. Intel особливо відверто висловлювалася щодо свого прогресу в постачанні електроенергії.

Коротше кажучи, сучасні процесори — це щільне гніздо нанорозмірних даних і проводів живлення, які прокладаються шар за шаром під час виготовлення.

Intel запропонувала подавати електроенергію з заднього боку чипа. Це має підвищити ефективність шляхом спрощення маршрутизації електроенергії.

У певному сенсі всі відносно легкодоступні способи нарощуання продуктивності були зібрані, і тепер розробникам чипів доводиться працювати більше, щоб досягати вищого рівня продуктивності. Звідси все починає ставати дивним.

До цього моменту передове пакування було в основному однорідним у тому сенсі, що один постачальник розробляв і впроваджував чипи. Це почне змінюватися, оскільки такі технології, як Universal Chiplet Interconnect Express (UCIe), відкривають двері для різнорідних пакетів.

Уявіть собі, що графічний процесор AMD і процесор Intel використовують спільний сокет. Чи стане реальністю цей конкретний приклад? Можливо, ні — технічно Intel і AMD вже пробували це, але це не спрацювало. Але UCIe відкриває двері для таких типів архітектур чиплетів, навіть якщо це створює нові проблеми на цьому шляху.

Навіть пластини, на яких упаковані ці чиплети, вивчаються повторно. Минулого року Intel оголосила , що працює над скляними підкладками, які можуть підтримувати більш щільні, гарячі масиви мікросхем без деформації. Як би дивно це не звучало, Intel каже, що до появи цієї технології залишиться лише кілька років.

Інші, тим часом, досліджують використання кремнієвої фотоніки як засобу переміщення даних між чиплетами. Використання кількох матриць дозволяє створювати більші, складніші процесори, але також створює труднощі щодо переміщення даних між їхніми блоками. Lightmatter’s Passage, Photonic Fabric від Celestial AI і TeraPHY від Ayar Labs — це кілька прикладів того, як люди намагаються пом’якшити ці проблеми, підвівши оптичні канали передачі даних безпосередньо до кремнію.

Незважаючи на те, що досягнення в технологічних процесах залишаються важливими, такі фактори, як упаковка, подача електроенергії та передача сигналів, є, мабуть, такими ж важливими, і з часом, можливо, ставатимуть ще більш важливими.

Тож, якщо хтось не натрапить на якесь дивовижне рішення для продовження зменшення розмірів транзисторів, виробництво чипів, щоб продовжувати збільшувати продуктивність, буде досліджувати різні технології, які сьогодні здаються дивними.

За матеріалами: The Register